低COP硅片(硅和SOI)

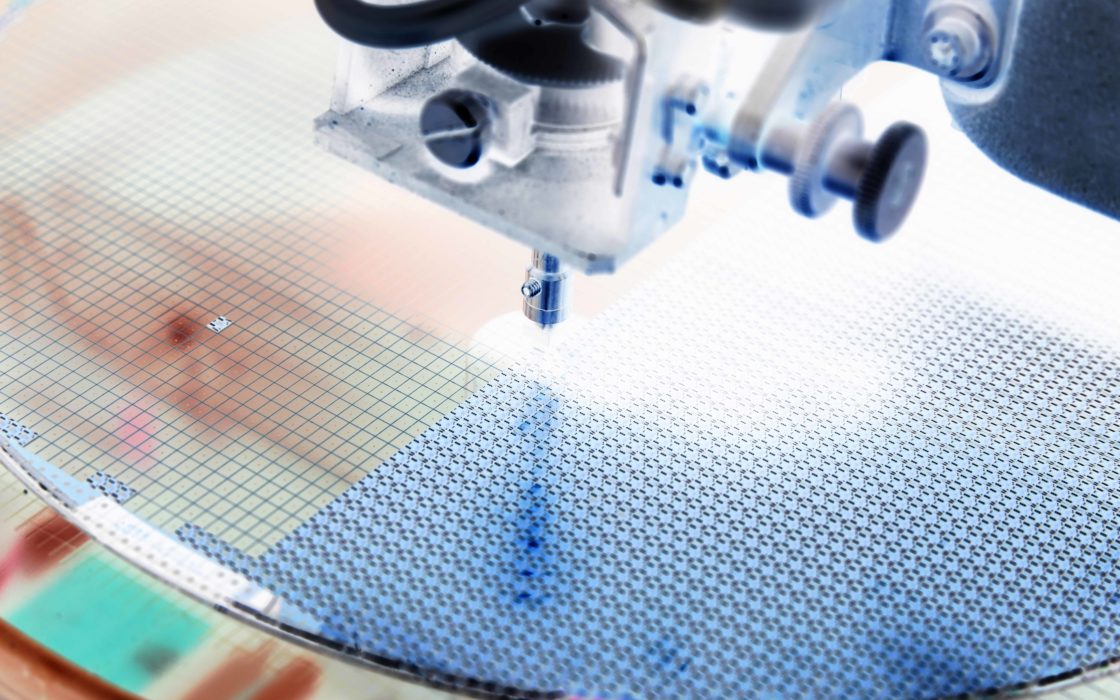

Okmetic的低COP硅片和SOI硅片具有最少量的临界尺寸晶体颗粒(COP),使其成为先进无外延功率IC器件的区熔硅片的优质替代品,且更具经济效益。Okmetic利用低COP的先进磁拉法(A-MCz®)晶体生长工艺,确保低COP硅片质量的同一性。

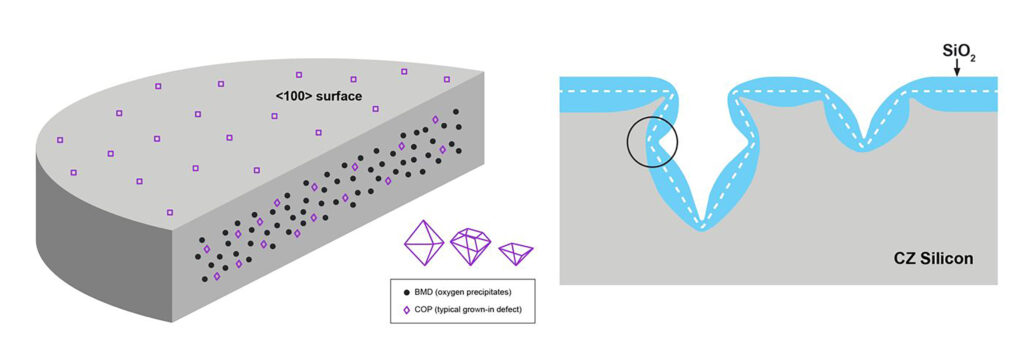

功率半导体领域的技术进步和成本效益要求推动了人们对于更薄栅极氧化物和提高良率水平的需求。Okmetic的低COP硅片能够有效地满足这些要求,其特征即在晶圆表面附近具有最少量的COP(源自晶体的颗粒)。众所周知,COP会对栅极氧化物完整性(GOI)的性能产生负面影响,这就是为什么它们的存在对于使用中高电阻硅片的功率器件来说是种挑战,这种中高电阻的硅片缺乏固有的无COP特性。

Okmetic的低COP硅片具有最少量的COP,能够满足功率半导体对更薄栅极氧化物和提高良率水平的需求。

Okmetic的低COP硅片采用我们标志性的先进磁拉(A-MCz®)长晶技术,经过优化后无需额外价格昂贵的退火工艺。Okmetic的低COP晶圆适用于电阻率为1欧姆-厘米及以上的200mm 功率分立器件硅片和电源管理SOI硅片。

增强GOI的性能

控制抛光片中与晶体相关的表面缺陷问题的主要难点在于,有效管理晶体生长过程中聚集的填隙和空位相关缺陷的生长。与空位相关的缺陷,譬如COP和FPD(流型缺陷),可能会导致器件制造过程中出现在近表面的问题。这些问题的示例包括GOI(栅极氧化物完整性)受损以及PN结中的电流泄露。

Okmetic的低COP硅片具有最少量的临界尺寸晶体颗粒(COP),从而确保了能够优化GOI的性能。通过结合低COP选项和BMD优化,我们能够进一步提高GOI的性能。Okmetic的低COP硅片是区熔法硅片的理想替代品,更具经济效益。它们特别适合先进的非穿通型(NPT)/场截止型(FS)IGBT器件,以及使用Okmetic电源管理SOI硅片的器件,譬如栅极驱动器和功率ASIC。

Okmetic的低COP硅片是区熔法硅片的理想替代品,更具经济效益。

无需外延沉积即可获得卓越的表面质量

Okmetic的低COP晶体生长方法能够降低总体拥有成本,并消除会引起滑移线的热应力风险,这种风险通常与传统COP退火工艺相关。

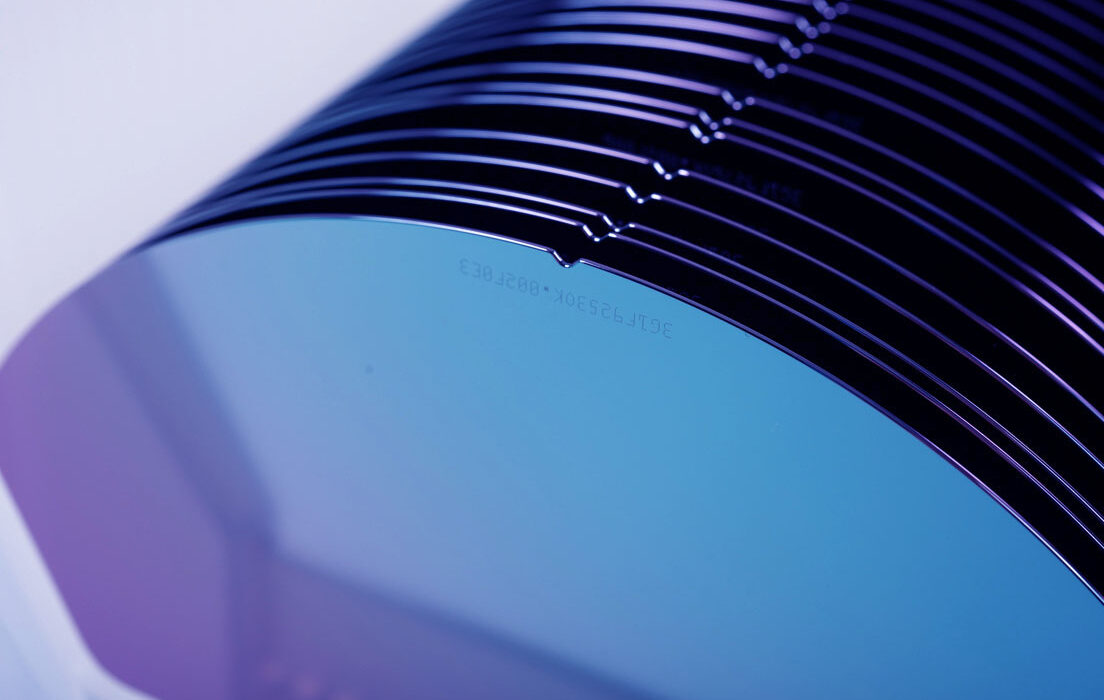

低COP性能适用于200mm、掺磷或掺硼的功率分立器件硅片和电源管理SOI硅片,其电阻率高于1欧姆-厘米。除此之外,晶圆定制的选项与标准COP硅片类似。譬如,电源管理SOI硅片也可以是低COP、无台阶型的。电源管理SOI硅片还提供采用退火工艺的零COP版本。

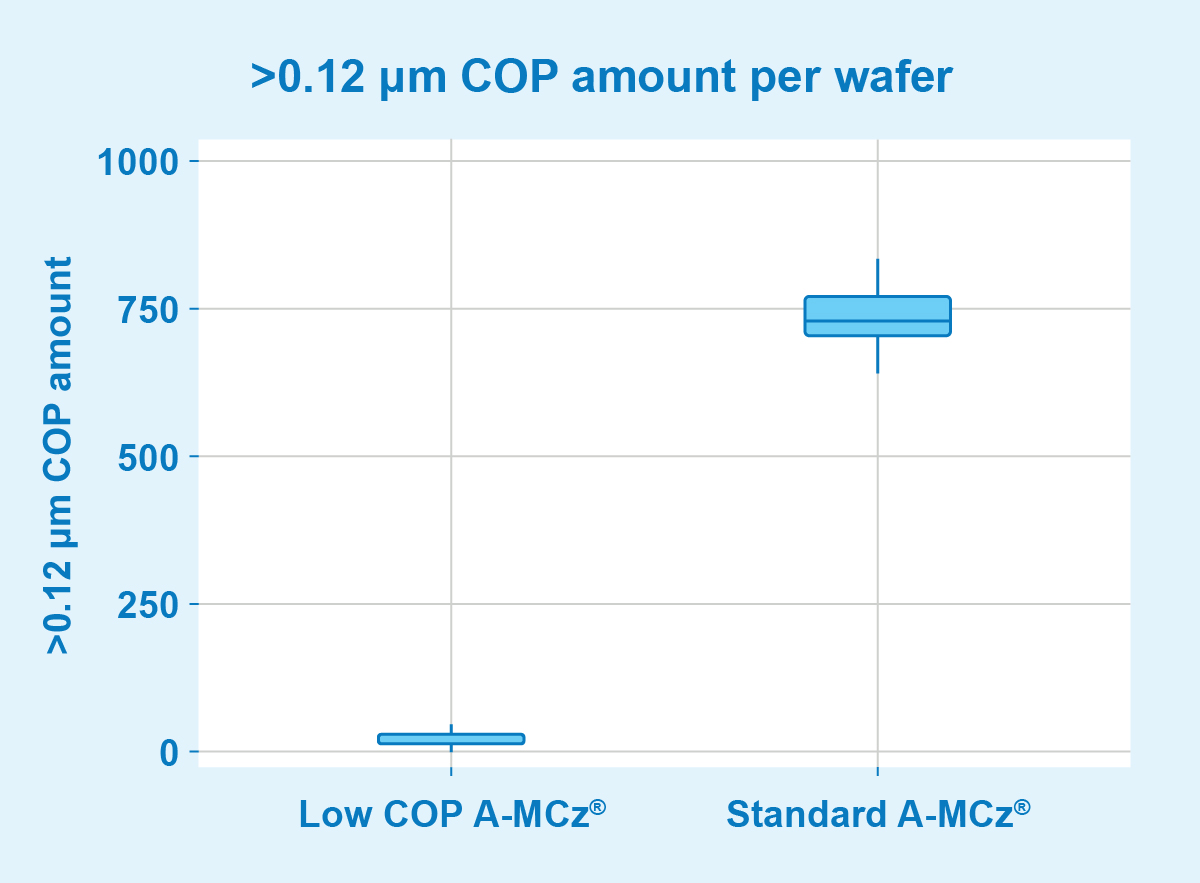

200mm硅片的COP含量比较

| 标准先进磁拉法(A-MCz®) | 低COP先进磁拉法(A-MCz®) | |

| COP >0.10微米 | <2000/每片硅片 | <500/每片硅片(通常约为300/每片硅片) |

| COP >0.12微米 | <1000/每片硅片 | <100/每片硅片(通常约为50/每片硅片) |

低COP硅片的常用规格

| 晶体生长方式 | 低COP先进磁拉法(A-MCz®) |

| 直径 | 200 mm |

| 晶向 | 目前晶向为<100>,后期将扩大范围至<110>和<111> |

| N型掺杂剂 | 磷 |

| P型掺杂剂 | 硼 |

| 电阻率1 | 1 至 >1,500欧姆-厘米 |

| 电阻率容差 | 根据价格目标和电阻率范围确定 |

| 径向电阻率梯度 (RRG)2 | 通常低于8% |

| 氧浓度 (Oi)3 | <4 至 14 ppma |

| 径向氧梯度 (ROG)4 | 通常低于10% |

| 碳浓度5 | <0.5 ppma |

| 单抛片厚度6 | 550 至 1,150微米 |

| 双抛片厚度6 | 380 至 1,150微米 |

| 单抛片背面处理 | 蚀刻、Polyback、LTO |

| COP含量7 | COP >0.12微米:<100个/每片硅片 COP >0.10微米:<500个/每片硅片 |

2SEMI MF84,取决于电阻率目标和边缘排除

3ASTM F121-831/SEMI MF1188-1107

4SEMI MF951,低氧浓度:ROG >20%

5ASTM F123-91,受测量技术限制

6在一定限制条件下可实现其他厚度

7SP1测量

完全兼容CMOS晶圆表面质量和清洁度要求

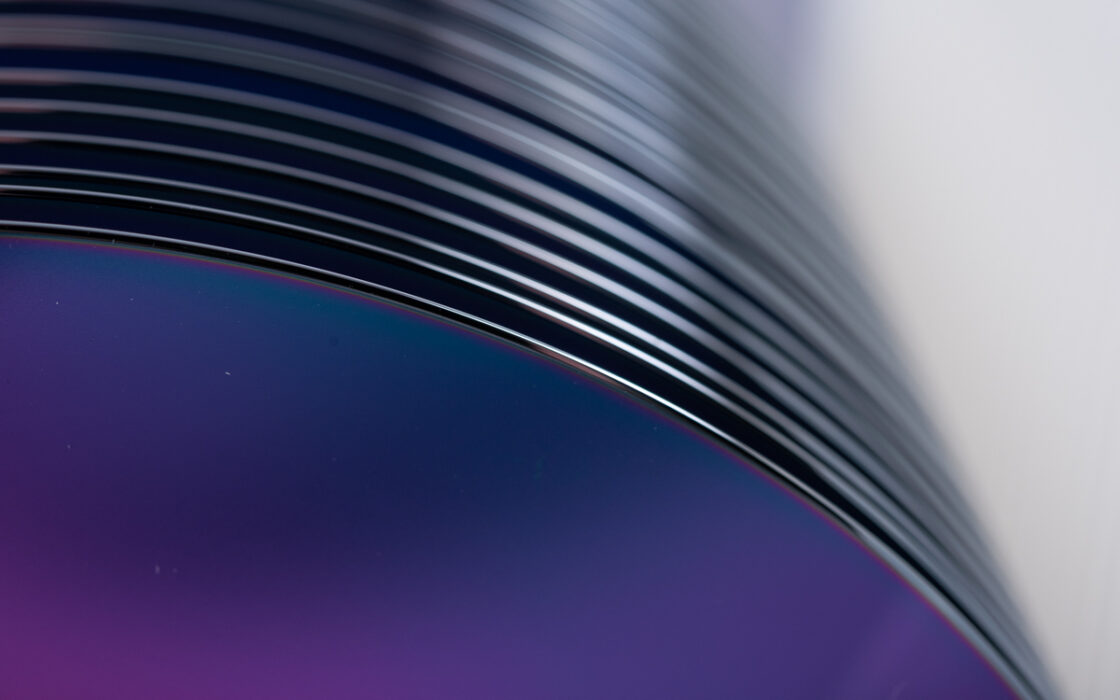

低COP的SOI硅片常用规格

| 晶体生长方式 | 低COP先进磁拉法(A-MCz®) |

| 直径 | 200 mm |

| 晶向 | 目前晶向为<100>,后期将扩大范围至<110>和<111> |

| N型掺杂剂 | 磷 |

| P型掺杂剂 | 硼 |

| 电阻率1 | 1 至 >1,500欧姆-厘米 |

| 电阻率容差 | 根据价格目标和电阻率范围确定 |

| 氧浓度 (Oi)2 | <4 至 14 ppma |

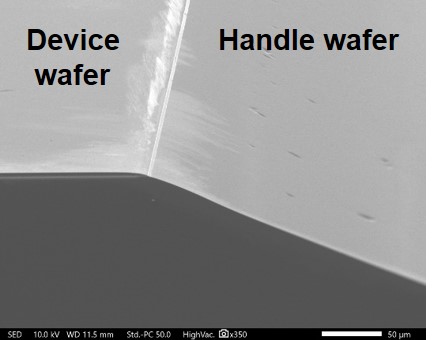

| 器件层厚度3 | 1微米至 >200微米(±0.1微米) |

| 埋氧层厚度4 | 0.3微米至 >5微米 |

| 底层硅片厚度5 | 300微米至950微米(±3-5微米) |

| 背面处理 | 抛光、蚀刻、氧化物或无氧化物 |

| COP含量6 | COP >0.10微米:<500个/每片硅片 COP >0.12微米:<100个/每片硅片 提供采用退火工艺的零COP版本 |

| 台阶区域7 | 标准或无台阶型(取决于硅片大小和厚度) |

2 ASTM F121-831/SEMI MF1188-1107

3 在一定限制条件下可实现其他厚度

4 类型:热氧化物。通常0.5微米至2微米,一定条件下可实现更厚的埋氧层。

5 200 mm:通常725微米,复杂器件有±3微米容差

6 SP1测量

7 提供200mm、725微米厚度的无台阶型版本

完全兼容CMOS晶圆表面质量和清洁度要求