# OKMETIC

# MORE DESIGN FREEDOM WITH BONDED SOI WAFERS

## **BSOI**

Fully customizable with thick or thin device layer. Suitable e.g. for traditional MEMS devices. Also advanced options such as two device and BOX layers of different thicknesses. Also available as Terrace Free version.

### E-SOI®

Highly uniform wafers with  $\pm 0.1~\mu m$  thickness variation. Suitable e.g. for silicon photonics and high-precision siliconbased MEMS. Also available as Terrace Free version.

## **C-SOI**®

Wafers with embedded / buried cavities. Suitable e.g. for pressure and inertial sensors, silicon speakers, ultrasonic transducers, resonators and microfluidic devices.

# TSV - Through Silicon Vias

Polysilicon filled TSVs enable isolated electrical connections to be made through silicon wafers.

# DESIGN FREEDOM, PERFORMANCE AND EASE OF MANUFACTURING

- Bonded SOI wafers provide an optimal platform for the manufacture of demanding MEMS, sensor, RF and power devices.

- Device manufacturers benefit from increased design freedom, maximum device performance, costeffectiveness and ease of manufacturing.

- Customized wafer solutions to meet your device and process needs.

- SOI wafer volume production for leading semiconductor device manufacturers since 2001.

- Fully in-house process covering crystal growth, wafering, SOI bonding, DRIE and lithography.

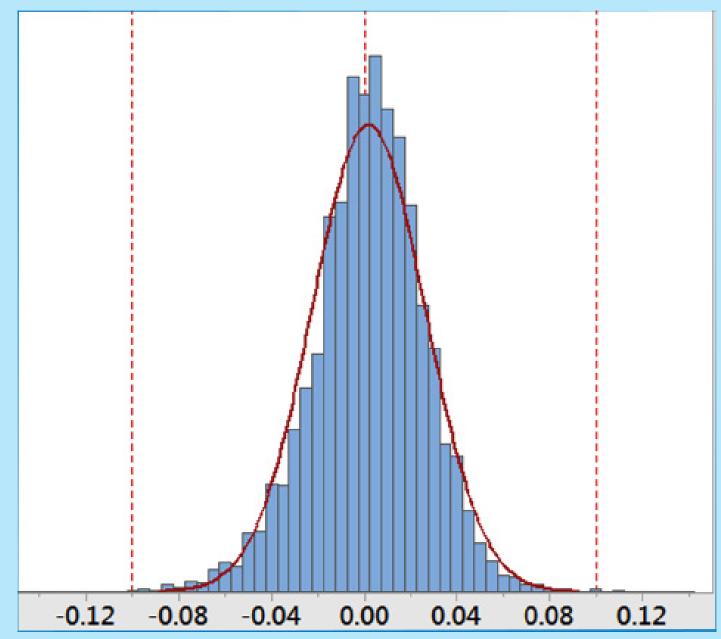

#### Device layer thickness capability of E-SOI® wafers

Deviation from target thickness (µm)

#### TYPICAL SOI WAFER SPECIFICATIONS

#### **RESISTIVITY**

From <0.001 to >7,000 Ohm-cm

#### **DEVICE LAYER THICKNESS**

From 1  $\mu$ m to > 200  $\mu$ m

Tolerance ±0.5 μm (standard BSOI), ±0.1 μm (200 mm E-SOI®), ±0.5 μm (C-SOI®)

#### HANDLE WAFER THICKNESS

From 300  $\mu m$  to 950  $\mu m$ , typically 725  $\mu m$  in 200 mm wafer and 380  $\mu m$  in 150 mm Back surface polished or etched

#### **BURIED OXIDE**

Type: thermal oxide, thickness: from 300 nm to 4 µm, typically between 0.5 µm and 2 µm