TSV wafers – Through Silicon Via

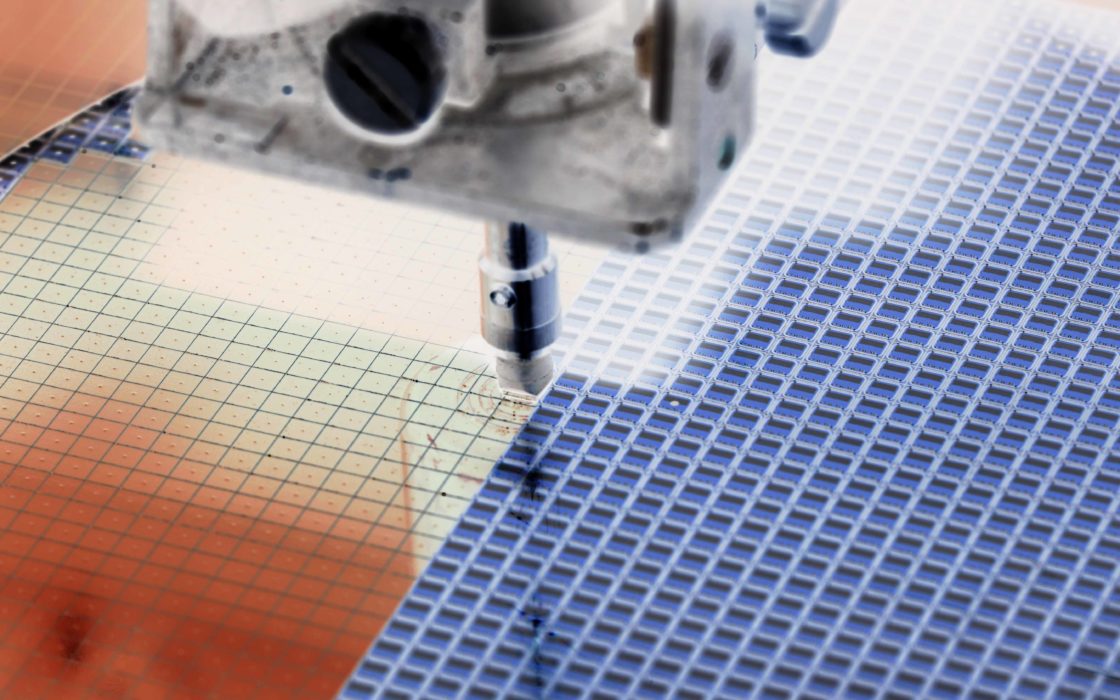

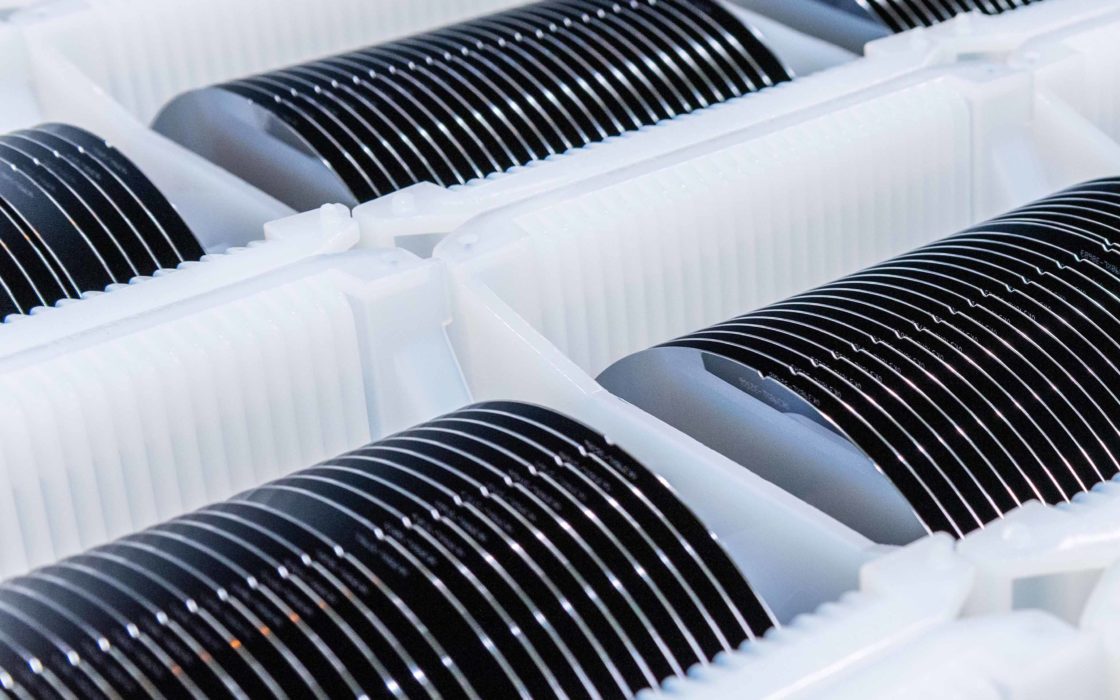

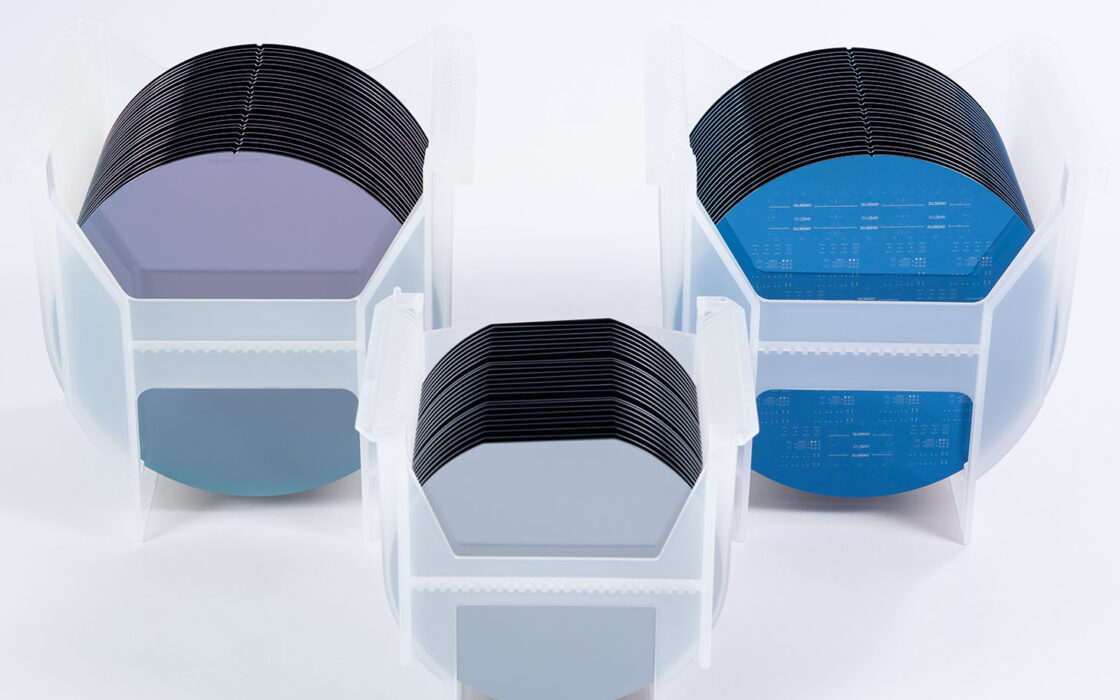

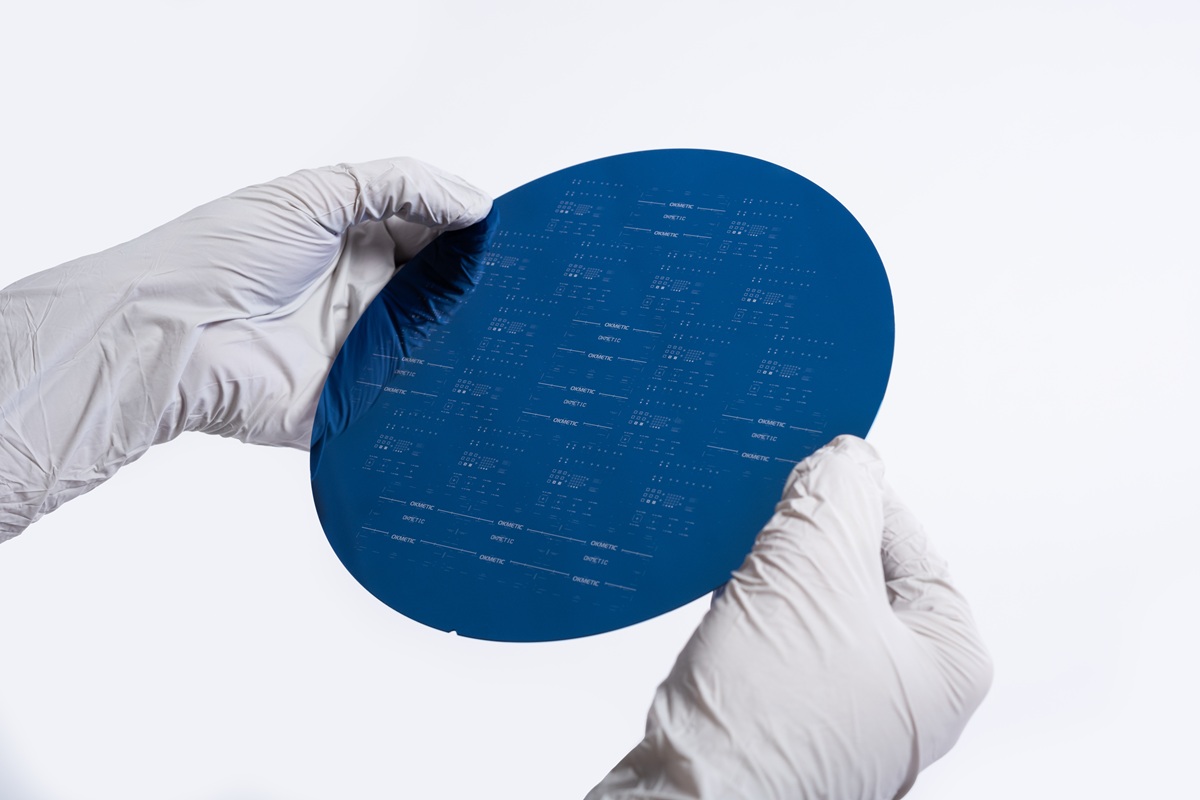

Okmetic wafers with polysilicon filled Through Silicon Via (TSV) enable 3D MEMS integration and advanced Wafer Level Packaging. Our TSVs are etched on Double Side Polished (DSP) silicon wafers and they are revealed later by back grinding process at the device manufacturer.

Okmetic polysilicon filled Through Silicon Vias (TSVs) enable isolated electrical connections to be made through silicon wafers, which help reduce the die size of MEMS devices and make interlayer electrical connections and 3D MEMS integration possible. Our silicon wafers with TSVs are used as interposers and capping wafers in variety of sensor applications such as resonators and inertial sensors.

Okmetic TSV wafers help reduce the die size of MEMS devices and enable interlayer connectivity and 3D MEMS integration

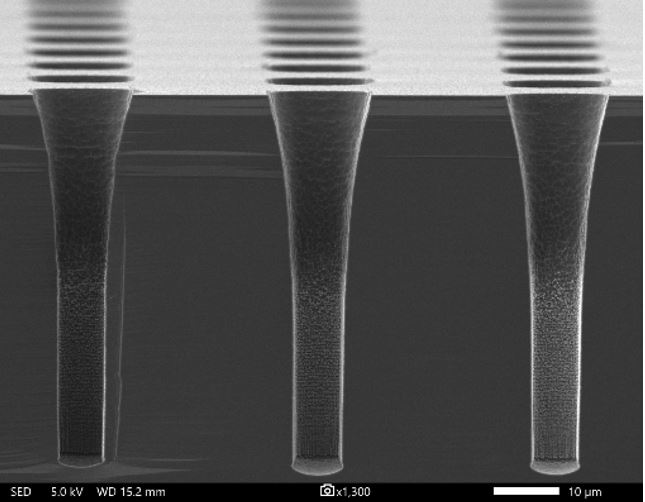

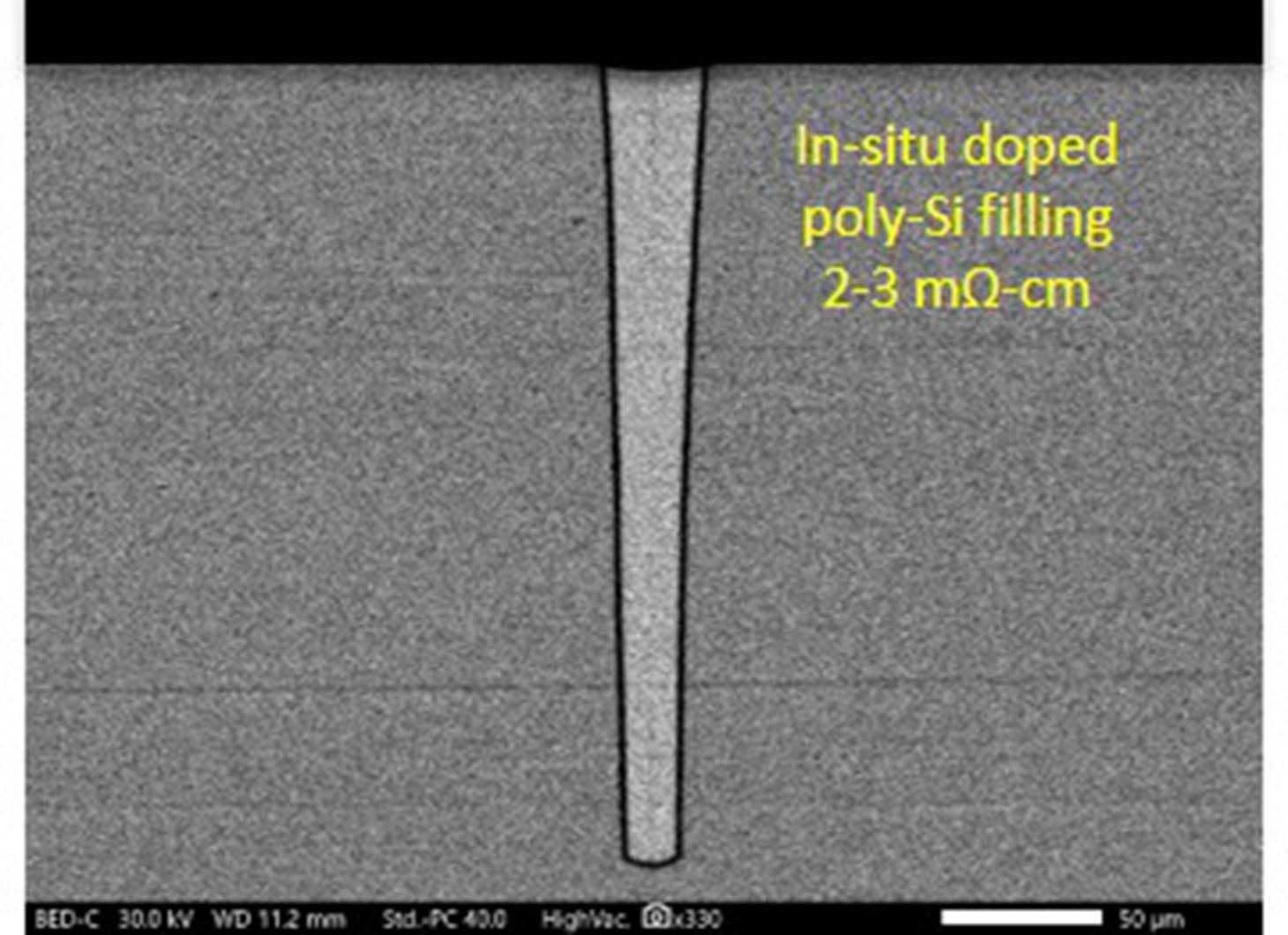

Okmetic TSVs are made with Via-First method by etching them on Double Side Polished silicon wafers and then using thermal oxide insulation and via/trench fill with in-situ boron doped polysilicon as interconnection material. This way TSVs are integrated to the wafer at a very early stage and the device manufacturers only have to reveal them with back grinding or other wafer thinning method in the further process. TSVs are also available without filling to allow device manufacturers the option to fill the vias according to their specific requirements.

The DSP wafers with Through Silicon Vias can also be combined with Silicon On Insulator wafer platforms. Customers can bond TSV wafers to other wafers with commonly used anodic, metal or glass frit bonding methods.

Combination of Through Silicon Via (TSV) wafers and C-SOI® wafers

Direct wafer level packaging of sensors requires vertical vias in order to use standard flip-chip assembly. In state-of- the-art MEMS production Cavity SOI (C-SOI®) wafers are combined with TSV wafers by bonding. This enables greatly simplified wafer-level packaging and heterogeneous chip integration. As a result smaller die size and cost-effective standard processes for capping and assembly are achieved.

Smaller die size and simplified process integration with TSV wafers

Okmetic TSV wafers with polysilicon filling are compatible with high temperature processes and their cleanliness fully meets CMOS manufacturing standards. Poly vias are robust and easy to integrate since they only consist of silicon and thermal SiO2 with well-known material properties. Customers can use well-established metallic interconnections and bumps in order to make electrical connections to poly-TSVs after bonding and thinning. Poly-TSVs have shown excellent performance in MEMS devices with their uniform resistivity, low via resistance and capacitance.

Demonstrated performance in MEMS devices:

- Resistivity uniformity <5% wafer to wafer and within wafer

- Resistance 10-15 Ohm (30 µm diameter, 200 µm depth)

- Capacitance <0.5 pF (2 µm thermal oxide insulation)

- Leakage current <0.5 pA@100 V (2 µm thermal oxide)

TSV wafer designs customized for your needs

Okmetic TSV’s are etched on Double Side Polished DSP wafers, which have excellent thickness uniformity and orientation accuracy, as well as first-rate crystal quality and homogeneity. Our highly experienced sales and technical support are happy to help you find an optimal solution and to discuss the TSV wafer requirements such as wafer thickness, via dimensions, pitch, resistivity, capacitance, layout and isolation resistance more in detail.

DSP wafers used for TSV, specifications

| Growth method | Cz, MCz, A-MCz® |

| Diameter | 200 mm, 150 mm |

| Crystal orientation | <100>, <110>,<111>, off-oriented |

| N type dopants | Antimony, Phosphorus, Red Phosphorus |

| P type dopants | Boron |

| Resistivity1 | From <0.001 to >7,000 Ohm-cm |

| Thickness2 | 625 to 1,150 μm |

| Thickness tolerance3 | ±5 µm |

| TTV | <1 μm or ≤0.7 μm |

| DSP orientation accuracy4 | ±0.2° |

| SFQR | ≤0.2 μm |

2Other thicknesses possible with certain limitations.

3±3 µm for demanding devices.

4±0.15° for demanding devices.

Full CMOS compatible metal impurity and surface quality levels

TSV design aspects

| Width | 7-30 µm |

| Length | >2x width |

| Depth | <250 µm |

| Aspect ratio | <10 |

| Via density | <20 vias/mm2 |

| Isolation oxide thickness | 0.5…2.0 µm |

| Via dishing | <0.5 µm |

| Via resistivity | <5 mOhm-cm (In-situ boron-doped polysilicon) |